Nova geração de sistemas ciber-físicos

O PPS3 está focado na criação de uma nova geração de sistemas ciber-físicos. Isto levanta diversos desafios, que estão atualmente a ser endereçados pelo projeto, nomeadamente:

- Perceção: relacionado com os sensores necessários para monitorizar o ambiente envolvente. Estes sensores têm de ter baixo consumo energético, serem compactos (tamanho pequeno) e baixo custo.

- Autonomia: relacionado com o consumo energético do sistema completo e com a tolerância a falhas durante operação. O aspeto importante deste desafio é assegurar uma operação de longa duração com uma pilha (para aplicações remotas) e garantir que o sistema não precisa de manutenção física (uso de atualizações over-the-air do firmware).

- Segurança: relacionado com a privacidade dos dados (encriptação de mensagens e validação da fonte de informação)

- Disponibilidade: relacionado com comunicação bidirecional em qualquer local.

- Adaptabilidade: relacionado com a capacidade de atualização e flexibilidade para endereçar diferentes casos de uso com uma mesma plataforma de hardware (através da atualização do firmware)

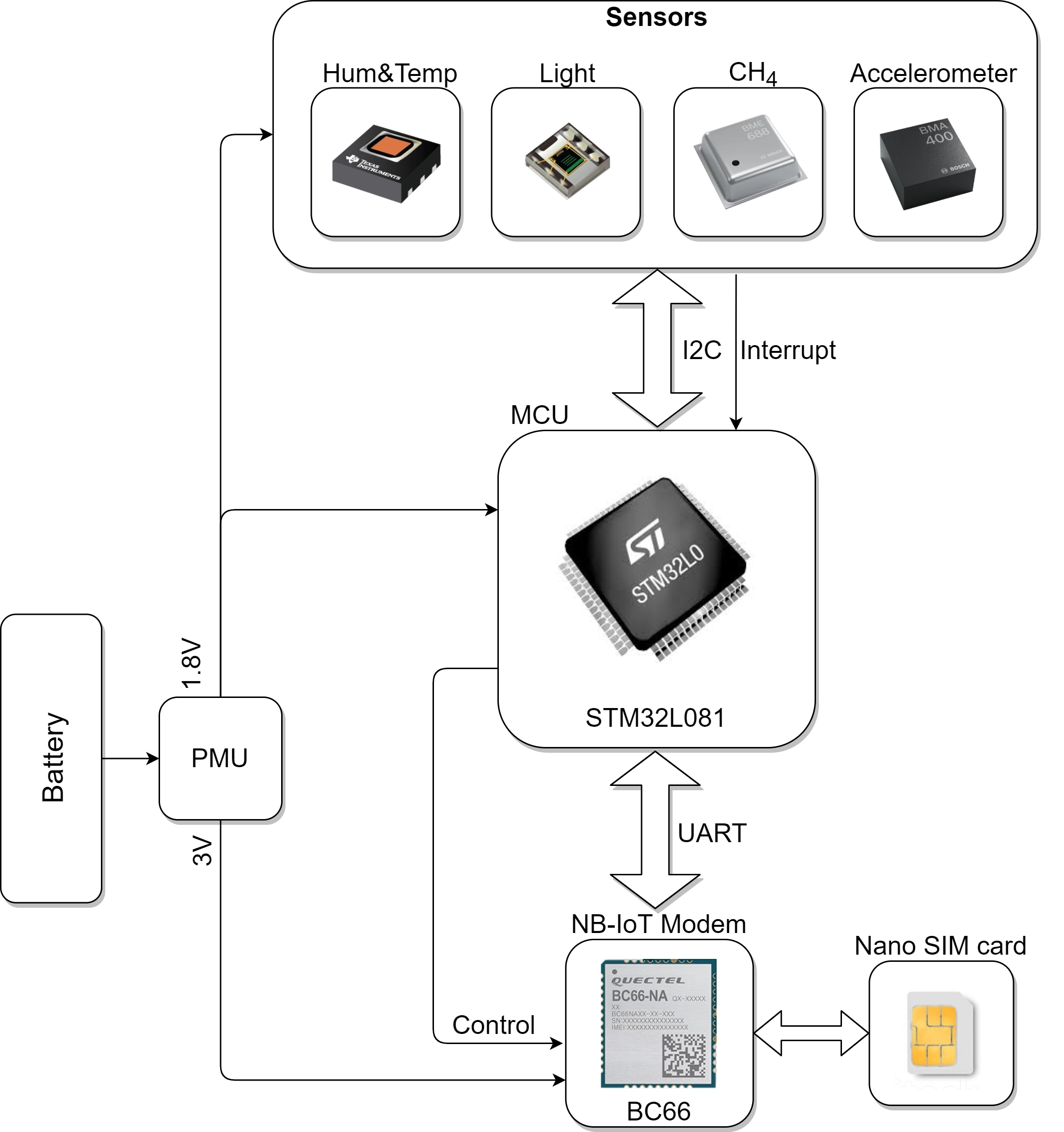

A arquitetura base do dispositivo pode ser vista na figura 1. O dispositivo é composto por: (i) sensores, para monitorização ambiental (temperatura, humidade, gás, vibrações/acelerações); (ii) um microcontrolador, para tratar do processamento, encriptação e armazenamento de dados; (iii) uma pilha, para alimentar o dispositivo e diferentes modos de operação que permitem reduzir o consumo energético; e (iv) um modem de comunicação, para tratar da transferência de dados.

Figura 1 – Arquitetura base do CPS

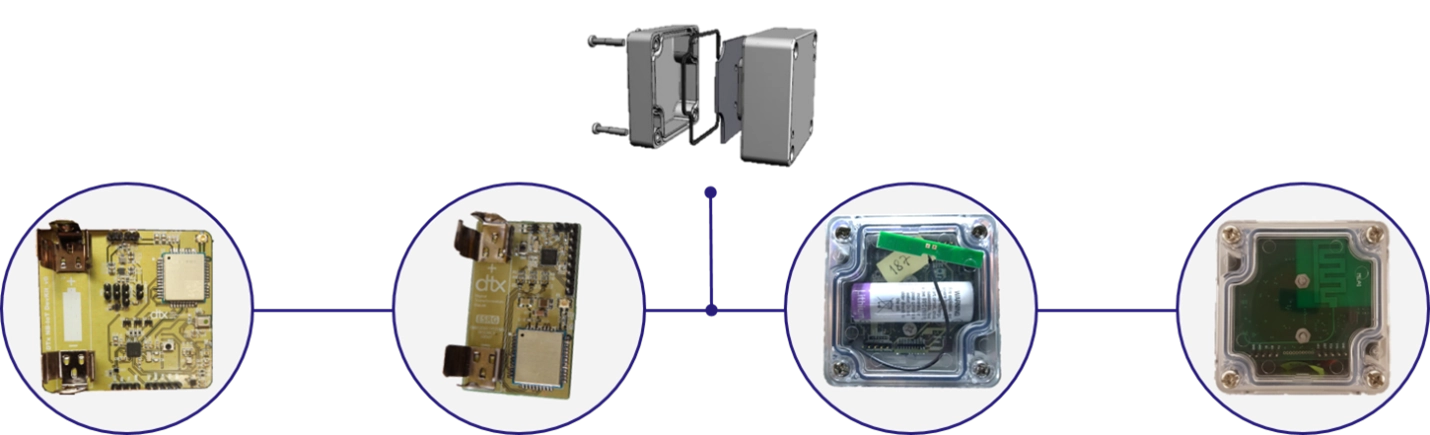

O projeto conta já com quatro iterações de hardware (ver figura 2). Da esquerda para a direita na figura, a primeira iteração focou-se na validação do sistema e das suas tecnologias. A segunda iteração tinha como objetivo melhorar o tamanho e custo de fabrico da solução. A terceira versão foi adaptada para encaixar no encapsulamento que seria utilizado em cenários com condições reais. A quarta versão permitiu testar o desenho de uma antena embebida na própria PCB, que poderia melhorar as comunicações. Presentemente o projeto encontra-se na quinta iteração, onde modularidade e imunidade a interferências magnéticas se encontra a ser implementado.

Figure 2 – CPS iterations

A par com as versões de hardware, também o firmware do dispositivo é continuamente atualizado. Começou com uma aplicação bare-metal que permitia ler os dados dos sensores e enviar imediatamente para a cloud e evoluiu para uma versão com FreeRTOS, numa tentativa de melhorar a modularidade da aplicação. No entanto os ganhos não foram notórios e optou-se por desenvolver uma nova versão bare-metal que permitia guardar os dados lidos pelos sensores e só enviá-los ao fim de um certo período de tempo, reduzindo, assim, o número de transmissões por dia e, consequentemente, o consumo energético total. Após esta iteração, foi adicionada encriptação aos dados a serem transmitidos, de modo a proteger as comunicações, uma vez que também se adicionou a possibilidade de configuração remota do dispositivo através de comandos enviados pelo servidor. Na última das iterações mais significativas, o ThreadX foi adicionado, permitindo retomar a ideia da segunda iteração, mas com ganhos bem mais notórios, permitindo reduzir o consumo energético e aumentar a modularidade do sistema, assim como o seu desempenho. Na versão mais recente foi ainda adicionada a possibilidade de fazer atualização ao firmware over-the-air, isto é, atualizar o firmware remotamente, sem necessidade de contacto físico com o dispositivo.

Os dispositivos desenvolvidos encontram-se neste momento numa fase de testes em cenários com condições perto das reais, para validação e melhoramento dos mesmos. Entretanto, uma outra linha de trabalhos procura migrar este mesmo sistema para plataformas FPGA e tecnologia ASIC, que permitem a fabricação em larga escala de um chip customizado para o LINK4S. Na fase atual dos trabalhos existem duas arquiteturas de processador a serem implementadas no microcontrolador customizado: Arm Cortex-M1 (otimizado para FPGA, seria substituído pelo equivalente Arm Cortex-M0+ se utilizado para fabricação de ASIC) e RISC-V (uma arquitetura open-source que permite a customização do próprio processador se necessário).

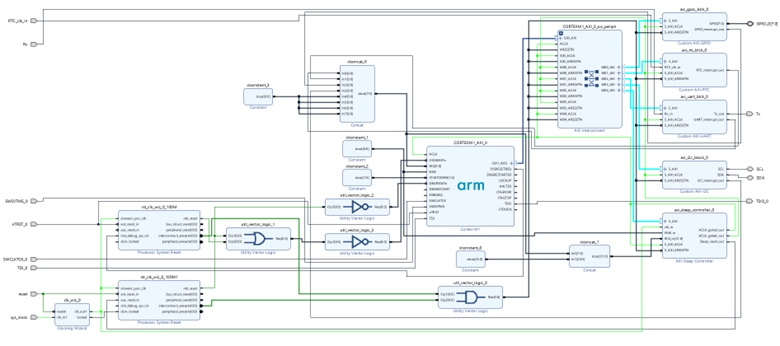

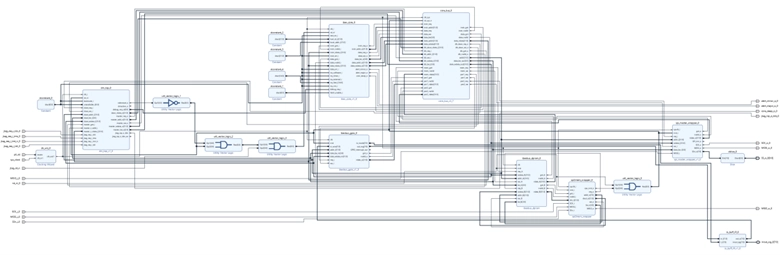

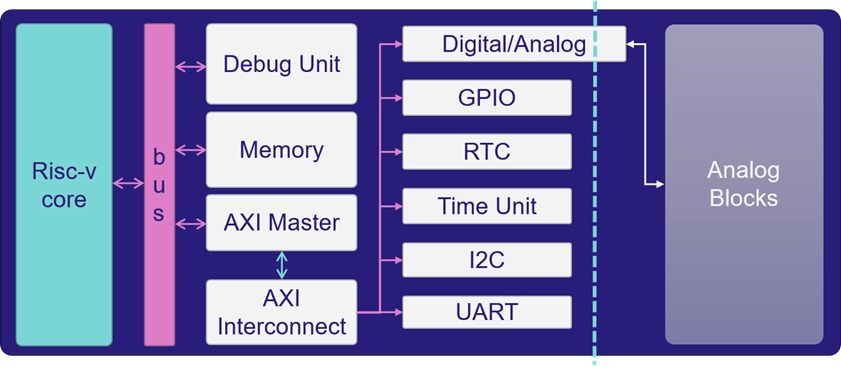

O sistema em FPGA com o Cortex-M1 já se encontra desenvolvido e validado com o restante hardware, replicando com sucesso a funcionalidade dos dispositivos já em testes. Este sistema possui apenas os periféricos necessários para as funcionalidades previstas e um sleep controller que permite replicar alguns modos de operação de consumo mais reduzido (ver imagem 3 para melhor perceção dos blocos que compõem o sistema em FPGA com Cortex-M1). Em paralelo está a ser desenvolvida a solução com recurso ao microprocessador baseado em RISC-V, que requer mais algum esforço de implementação relativamente aos periféricos necessários, mas permitirá uma transição mais fácil para o fabrico de ASIC (ver imagem 4 para melhor perceção dos blocos que compõem o sistema em FPGA com RISC-V no seu estado atual).

Figure 3 – Cortex-M1 FPGA block diagram

Figure 4 – RISC-V FPGA block diagram

Assim que os testes em FPGA com a arquitetura baseada em RISC-V estiverem concluídos, o sistema poderá ser migrado para a tecnologia ASIC. A arquitetura planeada para o microcontrolador em desenvolvimento, incluindo as componentes digitais e analógicas, está representada na figura 5.

Figure 5 – RISC-V based architecture for the customized microcontroller